# newsletter edacentrum 01/02 2017

edacentrum

**EORSCHUNGSTHEMENPA**

ntiertes Design

Projektspiegel: Projektbericht

NEREID: NanoElectronics Roadmap for Europe: Identification and Dissemination

Roadmaps: eDesign 2018–2022 und Electronic Components & Systems Strategic Research Agenda (ECS-SRA) Forschungsthemen für anwendungsorientiertes Design elektronischer Komponenten und Systeme für Deutschland und Europa

Veranstaltungen: Rückblick auf den ADTC & edaWorkshop17, edaForum17 und das dritte edaBarcamp Ein europäisches "Familientreffen" rund um Elektronik, Design und Anwendungen und ein Blick in die Zukunft der Mikroelektronik

# NEREID: NanoElectronics Roadmap for Europe: Identification and Dissemination

Coordination Action (CA) within the Horizon 2020 ICT Work programme shows first results, but there are still things to be done...

NEREID is a Cooperation and Support action that has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 685559, with the objective to develop a roadmap for the European Nanoelectronics industry, starting from the needs of applications and leveraging the strengths of the European eco-system. In addition, it will aim to an early benchmark/ identification of promising novel technologies in nanoelectronics, and identify bottlenecks all along the innovation value chain.

Highlights of the NEREID project, which has a duration of three years, are three general workshops aiming at gathering the needs of the main application sectors, and specific workshops that will define the roadmaps of the different technology domains, with a broad involvement of leading experts from industry and academia. In September 2017, the project has published the first version of its roadmap on the future of European Nanoelectronics which is roughly summarized in this report.

# I. Introduction

The H2020 NEREID Coordination and Support Action (n° 685559) entitled "NanoElectronics Roadmap for Europe: Identification and Dissemination" has been funded by the European Commission following the Nanoelectronics call "H2020-ICT-2015 Generic microand nano electronic technologies" and has been launched at the European Nanoelectronics Forum in Berlin in December 2015 for a duration of 3 years.

The objective of NEREID is to develop a new roadmap for nanoelectronics, focused on the requirements of European semiconductor and applications. It will address societal challenges following advanced concepts developed by Research Centres and Universities in order to achieve an early identification of promising novel technologies covering the R&D needs all along the innovation chain. The final result will be a roadmap for European micro- and nanoelectronics, with a clear identification of medium and long term objectives.

In September 2017, the first version of this roadmap – referred to as Mid-Term-Roadmap – has been published. It has been elaborated by the project consortium during the first 18 month of the project in order to be able to publicly discuss this first version in order to identify possible improvements. This article is about to characterize the NEREID project and its Mid Term Roadmap.

# II. Mid Term Roadmap

The Nereid roadmap for nanoelectronics is dedicated to be used as input for future research programmes at European and National levels in order to join our effort to overcome the main challenges in nanoelectronics and put the EU at the forefront of future technological developments. Therefore it takes into account the specificity of the European industrial and academic landscape, and helps to better coordinate academic and industrial research for equipment, semiconductors and application developments.

# Character of the Roadmap

The NEREID roadmap is divided into several main technology sectors: Advanced Logic (including Nanoscale FETs and Memories) and Connectivity, Functional Diversification (Smart Sensors, Smart Energy, and Energy for Autonomous Systems), Beyond-CMOS (Emerging Devices and Computing Paradigms), Heterogeneous Integration and System Design, Equipment, Materials and Manufacturing Science, and also includes cross-functional enabling domains.

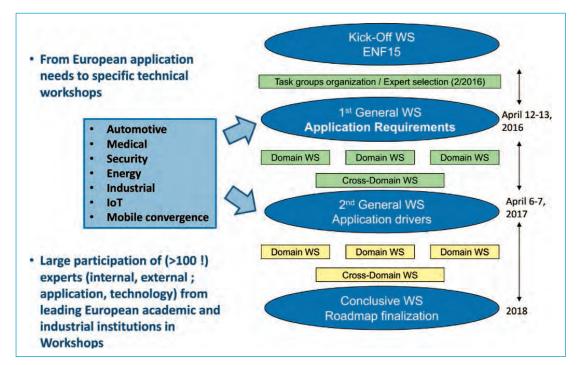

The roadmap's content started from knowledge coming from several different very important European application areas like Energy, Automotive, Medical/Life science, Security, IoT/Smart connected objects, Mobile convergence and Digital Manufacturing (s. Figure 1.01).

The NEREID Roadmap, focused on medium and long term time horizons, is complementary to the industry driven AENEAS Strategic Agenda, the ECSEL Funding Label: ICT-CSA-685559

**Runtime:** 15/11/2015 – 14/11/2018

Homepage: www.nereid-h2020.eu

Project partners AENEAS, CEA-LETI, IUNET, EPFL, edacentrum, Fraunhofer, ICN2, Grenoble INP, SINANO, imec, PoliTo, VTT and Tvndall

Figure 1.01: The NEREID roadmap flow and the difference to other activities

EREII

MASRIA and the currently developed ECS Strategic Research Agenda, which are focusing on shorter terms (s. Figure 1.01). The NEREID Roadmap is feeding the longer term part of the ECS SRA. Besides the timescale, the NEREID Roadmap differs to the other agendas with respect to topics (no chapter dedicated to applications while applications are considered initially and "in the background"), method (s. below) and the treatment of figures of merit (more detailed view). Additionally the NEREID Roadmap covers the whole range of TRL's, starting with TRL 1 as the work is led by academia and not primarily industry-driven (although, for each WP, there is an industrial co-leader, and the contributors come from both communities).

NEREID has some commonalities and is developing joint collaboration with the new International IRDS Roadmap (IEEE International Roadmap for Devices and Systems) especially in the fields of More Moore, Beyond CMOS and computing systems. However, it is also complementary to IRDS with very important NEREID activities in the More than Moore domain (e.g. Smart Sensors, Smart Energy, Energy Harvesting), which is a sound European competence, leading to a large diversity of electronic systems useful for many applications (s. Figure 1.01). In the More Moore field, there are also strong interests in Europe for specific activities dealing with very low power systems, leading to possible disruptive applications for instance for future IoT systems.

Understanding the dependencies between short/ medium term (e.g. More Moore and More than Moore) and long/very long term (e.g. Beyond CMOS) activities is very important to speed-up technology transfer between academia and industry. Using disruptive technologies leads to possible new large future markets. Therefore, the Nereid Roadmap takes into account the specificity of the European industrial and academic landscape. It and will be very important to better coordinate academic and industrial research for equipment, semiconductors and application developments. Further it serves as input for future research programmes at European and National levels. It is a guideline to coordinate joint efforts to overcome the main challenges in nanoelectronics and put the EU at the forefront of future technological developments.

# Method to Build the Roadmap

The project solicits application and technology experts from leading industrial and academic research organizations to present the state-of-the-art to identify and collect application knowledge potential users of the nanoelectronics technologies. They participate in General and Domain (WPs) Workshops (s. Figure 1.02). Three major general Workshops and many Domain Workshops (for WPs and Tasks) are organized with a large participation by application experts/technology users and technological experts (more than 100 experts).

The experts provided insight on the technology requirements in terms of both performance and timescale for the future applications and/or (generic) functions envisioned by their companies. These requirements have been used afterwards by technology experts for the identification of the most promising technologies and functions that can satisfy the functionalities and performances needed for the different applications. These Workshops allow the consortium to better define the technology roadmap according to application requirements (in the fields of Energy, Automotive, Medical/ Life science, Security, IoT/Smart connected objects, Mobile convergence, Digital Manufacturing) and technology evolution (Advanced Logic and Connectivity, Functional diversification, Beyond-CMOS, Heterogene-

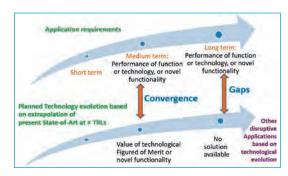

Figure 1.02: The NEREID roadmapping method/process

Figure 1.03: The NEREID roadmapping approach

ous Integration and System design, Equipment, Materials and Manufacturing Science). Structured discussion and debate provide the convergence between applications and technologies, as shown in Figure 1.03

The proposed idea is that the scenarios of evolution of the products/applications will result in performance evolution scenario for the functions, which could be generic enough to be applied to many products. The next step in the roadmapping process is to derive, from the evolution of functions, the evolution of the underlying technologies and devices using the expertise of technology experts. Insights on future technology evolution and availability can also prompt new ideas for disruptive products and applications, which are discussed in Domain Workshops and are also presented by technology experts during the General Workshops.

This common work between technology and application experts leads to the early identification of the most promising technologies needing additional R&D actions, which could be very useful for the future electronic products of European companies leading to a strong impact on the European economy and society.

# Societal benefits of a new European roadmap

Future electronic systems will play a vital role in all of the European key application areas mentioned above. The world of connected objects and the development of "Smart Everything Everywhere", with large future markets, imply the development of dedicated technologies like low power devices and the development of many new functionalities for sensing, computing, communicating, energy harvesting, etc.

The use of renewable energy sources is becoming one of the most important topics in our society. Among the benefits, it is possible to envisage the development of autonomous, wearable, or even implantable sensor nodes for health applications or environmental monitoring for instance. The development of "green" materials, replacing toxic/rare materials used nowadays, is also of paramount importance for future sustainable systems and society.

On the other hand, the estimated energy savings potential that can be achieved by introducing power electronics into systems is enormous, estimated at more than 25% of the current electricity consumption in the EU countries. Since power electronics is a key technology in achieving a sustainable energy society, the demand for power electronics solutions will show significant growth in the coming decades.

In the health sector, the strong incidence of chronic diseases, such as cancer, cardiovascular diseases, obesity, diabetes and autoimmune and psychiatric diseases will increase the demand for diagnostic devices (activity trackers, body monitors and multi-parameter real-time sensing). For most devices a low-cost, portable and fast diagnostic solution does not exist in the market yet. Moreover, devices could also serve to detect the incidence of health hazards caused by pollution (air quality, water and food monitoring ...) and address rising concerns about health and well-being. These emerging medical devices (wearable sensors, implantable sensors and others) would benefit healthcare facilities and support the acceptance of personalized, more-efficient medicines.

Connectivity functions will be everywhere in the future connected world, from the physical world, things and the persons, the autonomous objects, factory 4.0, to the cloud.

An early consideration of all these trends, which are taken into account in the NEREID Roadmap, will be beneficial to the EU. NEREID will lead to disruptive technologies and applications and many new markets, strengthening the international position of the European economy and having a great potential impact on the European society.

# Interactions with other international activities

The activities of NEREID strongly benefit from the international context of roadmapping through the Advisory Board that include personalities involved in USA and Asia in similar activities. They are proving systematic feedback about the coherence and complementarity of NEREID with the global context, while constructively recognizing the European focus on priorities, specific to NEREID.

On the other hand, NEREID has concretely started and implemented a series of actions of reciprocal benefits with the International Roadmap of Devices and Systems (IRDS). In fact, almost simultaneously with the launch of NEREID, in May 2016, IEEE announced the formation of the IRDS under their sponsorship to addresses the mapping of the ecosystem of newly reborn electronics industry. The migration from ITRS (International Technology Roadmap Semiconductors) to IRDS is currently proceeding seamlessly, with all reports produced in the past by ITRS 2.0 representing the starting point, and including contributions and groups from USA, Asia and Europe. This was a unique opportunity for NEREID to forge a partnership with IRDS, have reciprocal participations in meetings, and build a vision of the future of nanoelectronics, to which each initiative contributes with its specific strong points. Of particular importance is the concrete actions taken to compare roadmaps between NEREID and IRDS in the following fields, in which the interests of the two initiatives overlap:

- » Systems and Architectures: Cloud computing, IoT, Smartphone, Cyber Physical systems,

- » Outside System Connectivity: RF & Analog & Mixed Signal, Photonic Interconnects,

- » Beyond CMOS: Emerging memory and storage devices, Emerging information processing and logic devices, Emerging devices for functional diversification, Interface between emerging devices and novel computing architectures/paradigms,

- » Metrology,

- » Yield,

- » More Moore: Logic technology, Memory technology, Interconnect technology,

- » Factory Integration.

Furthermore the NEREID consortium is tightly connected by the participating experts to a common initiative of AENEAS, ARTEMIS-IA and EpoSS, who currently elaborate a new Electronic Components and Systems Strategic Research Agenda (ECS-SRA).

# III. Sectors of the Nanoelectronics Roadmap for Europe

The Nanoelectronics Roadmap for Europe concentrates on the following main nanoelectronics technology sectors, namely:

- » Beyond-CMOS,

- » Advanced Logic and Connectivity: More Moore (Innovative FETs and Memories) and Connectivity (Wireline and Wireless),

- Functional diversification: Smart Sensors, Smart Energy and Energy for Autonomous Systems,

- » System Design and Heterogeneous Integration,

- » Equipment and Manufacturing Science.

In the NEREID roadmap, each of these technology sectors are examined in separate work packages and described respectively by the following categories:

- » Relevance and competitive value

- » Vision

- » Scope and ambition

- » Main Concepts

- » Synergies with other topics (WP topics, if applicable)

Each technology sector's chapter is further amended by an executive summary and includes explicit recommendations.

The common work between technology and application experts documented in the Mid Term Roadmap is leading to the early identification of the most promising nanoelectronics technologies, which are needed for the future electronic products of European Companies leading to a substantial impact on the European economy and society. In the following, the roadmap content for these technology sectors is roughly summarised.

# IV. Beyond-CMOS (WP2)

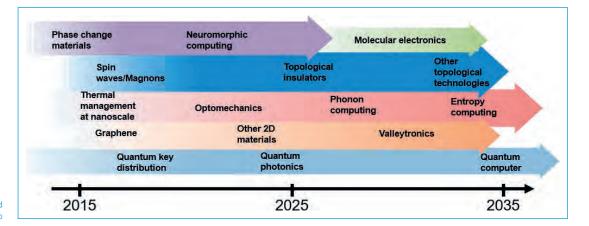

The Beyond CMOS chapter surveys the potential of the emerging technologies, new state variables and computing paradigms to provide efficient approaches to information processing, either for distributed computation within the expanding IoT or to realise accelerators on CMOS platforms to increase the processing speed. The focus is also on more fundamental issues like heat dissipation at nanoscale which has turned out to be the most critical bottleneck in information processing. Figure 1.04 gives an estimation of the Beyond CMOS roadmap.

This chapter deals with "Non-conventional information processing approaches and devices", focusing on the technology aspects of emerging information processing methods, and with "Designs and architectures for non-conventional information processing", concentrating on the potential of these new technologies for information processing and computing. The role of design and architectures (see chapter on system design and heterogeneous integration) is crucial in emerging computation paradigms.

Figure 1.04: Estimated Beyond CMOS Roadmap

# I Projektspiegel | newsletter edacentrum 01/02 2017

# Main concepts on Beyond CMOS research

The examined main concepts within the roadmap chapter on Beyond CMOS are 1) Quantum Photonics, 2) Spintronics, 3) Neuromorphic computing, 4) Thermal, Brownian and nanomechanical computing and 5) Steep-slope devices for emerging energy efficient computation paradigms.

# Recommendations for Beyond CMOS research

A thread running through most of the alternative computing approaches is the need to understand at conceptual, experimental and technological levels the thermal properties of materials and interfaces involved. This is currently a handicap ("show stopper") in the form of heat dissipation in almost all current and emerging technologies. Thus, a shift of paradigm in the perception of the thermal management challenge is needed. Europe has the potential to lead in this field and, consequently, to remove this roadblock.

In Silicon CMOS technology the heat dissipation challenge has led to "Dark Silicon", use of many-core units and to saturation of the operation frequency to a few GHz range, limiting the full exploitation of the potential of CMOS circuitry. In the long term, thermal issues can be transferred to Brownian or entropy computing and used either on their own or in a hybrid approach with other state variables. Capitalising on the wave nature of thermal vibrations is very challenging but it offers a potential alternative to very low power information processing. Nevertheless, at the moment embryonic efforts in this direction are few and pursued by fragmented communities, each excellent in their own right.

In the near term, neuromorphic computation holds a high promise in applications such as the IoT and big data. The field is making strong progress in algorithms and, to a lesser extent in hardware realisation. There are several technology candidates and the planned FET CSA may well accelerate progress in the Human Brain flagship project, in ICT LEIT projects and future constellations. Nevertheless, a directed programme towards neuromorphic hardware development in Europe is recommended.

Si-based quantum photonics must be an integral part of the Quantum Technology flagship, building on the European leadership in the field, already breaking frontiers in chip-level integration and competing globally in innovations, for example, with nanophotonics-based components such as single photon detectors based on superconducting nanowires.

Regarding Spintronics, memory cells are already in the market, and spin/charge-based devices, such as spin torque and spin Hall devices, are being developed. Moreover, there is also potential to create neuromorphic circuits using Spintronics. Magnons or spin-waves provide an interesting possibility for ultra-low power and very fast devices, and some logic elements, like majority gates, have already been demonstrated. Therefore, coordinated efforts in Magnonics are recommended.

The range of materials under investigation within alternative computing paradigms goes well beyond Silicon, e.g., in quantum (Nano) Photonics, neuromorphic computing and Spintronics. Steep slope devices are no exception. Thus, advances are urgently needed with technological figures of merit in mind of several nonsilicon based materials, ranging from scalable material production technologies, through wafer-scale nanofabrication with innovative tools and last but not least, a combined effort from the start with the design and architecture community.

# V. Advanced Logic and Connectivity (WP3): More Moore (Innovative/Nanoscale FETs and Memories) (T3.1)

The historical trend in micro/nano-electronics over the last 40 years has been to increase both speed and density by scaling down the size of electronic devices, together with reduced energy dissipation per binary transition, and to develop many novel functionalities for future electronic systems. We are facing today dramatic challenges for More Moore and More than Moore applications: substantial increase of energy consumption and heating which can jeopardize future IC integration and performance, reduced performance due to limitation in traditional high conductivity metal/ low k dielectric interconnects, limit of optical lithography, heterogeneous integration of new functionalities for future Nano systems, etc.

Therefore many breakthroughs, disruptive technologies, novel materials, and innovative devices are needed in the next two decades.

With respect to the substantial need for reducing the static and dynamic power of future high performance/ ultra-low power Tera scale integration and autonomous Nano systems, new materials, ultimate processing technologies and novel device architectures (FDSOI, FinFET, Nanowire FET, Non-charge-based Memories, and 3D integration) are mandatory. For different applications using such ultimate CMOS new circuit design techniques, architectures and embedded software are to be developed. The chapter focuses on the main trends, challenges, limits and possible solutions for future high performance and ultralow power nanoscale devices in the CMOS arena (s. Figure 1.05).

# Main concepts on Advanced Logic (Nanoscale FET)

The examined main concepts within the roadmap sub-chapter on Advanced Logic (Nanoscale FETs) are 1) Nanowires, 2) FDSOI, 3) FinFET, 4) Memories, 5) 3D sequential integration, 6) Modelling/Simulations Tools and 7) Characterization Tools.

|                   | 10nm                                          | 17nm           | 5nm           | 3nm |           |

|-------------------|-----------------------------------------------|----------------|---------------|-----|-----------|

| Fin-FET           | Co-integration of different channel materials |                |               |     |           |

|                   | Improve analog performance                    |                |               |     |           |

|                   | Subthresh                                     | old slope cont | rol           |     |           |

| R.RET             | Variability                                   | control        | $\geq$        |     |           |

|                   | 22nm                                          | 14nm           | 10nm          | 7   | nm        |

| FD-SOI            | Compatibility with different options          |                |               |     | $\supset$ |

|                   | Integration of new materials                  |                |               |     |           |

|                   | Ultra-Low Power design                        |                |               |     |           |

|                   | 3-D integra                                   | tion           | >             |     |           |

|                   | 7nm                                           | 5nm            | 3nm           | 2nm | 1nm       |

| NW-Nanosheet      | New materials                                 |                |               |     | $\geq$    |

| -                 | New geometries                                |                |               |     |           |

| The second second | Strain engi                                   | neering        | $\rightarrow$ |     |           |

|                   | 3-D proces                                    | s control      | $\geq$        |     |           |

| Sequential 3D        | Ultra-fine grain interconnections between layers                          |  |  |  |

|----------------------|---------------------------------------------------------------------------|--|--|--|

| 行击                   | Thermal management/self-heating mitigation                                |  |  |  |

|                      | Design Tools for place and route                                          |  |  |  |

| 1 mil                | Manufacturing challenges                                                  |  |  |  |

| Non Charge-based     | Threshold spread and variability control                                  |  |  |  |

| memories<br>OxRAM 📥  | Reliability and thermal stability                                         |  |  |  |

| CBRAM                | Cell architectures for scalability                                        |  |  |  |

|                      | New materials                                                             |  |  |  |

| Charact. & Modelling | Modelling and charact. of new materials, including confined ones (2D, 1D) |  |  |  |

|                      | Modelling and charact. of technology and process including 3D             |  |  |  |

|                      | Modelling and <u>charact</u> , of variability and reliability             |  |  |  |

|                      | Models and charact. of novel device concepts                              |  |  |  |

Figure 1.05: Nanoscale FETs: Research highways

# Recommendations for Advanced Logic (Nanoscale FET)

- » For Nanowires, identify the best material and geometry options for logics (high-speed as well as low-power), develop millimetre wave front-ends with III-V MOSFETs (applications for communication, radar), and consider the 3D aspects of processing.

- » For FD SOI, develop differentiated options (RF, Embedded Memories, and Imaging or molecules sensors) on FDSOI (applications for automotive, IoT, smart sensors...), ULP design (Vd<0,4V) for IoT market (wearable, medical...), and 3D integration for future neuromorphic and quantum computing approaches.

- » For FinFET, develop co-integration of different channel materials, low contact resistivity and high strain solutions, improve FinFET analog performance.

- » For non-charge-based Memories, overcome the HRS broadening for OxRAM, improve the process for GST patterning for PCRAM, and develop new materials enabling horizontal scaling.

- » For 3D sequential integration, define which applications will benefit from very high density intercon-

nections (IOT, neuromorphic...), and develop a 3D place and route tool.

» For Modelling/Simulation and Characterization, develop new tools taking into account all the new materials, technologies and device architectures in order speed-up technology optimization and reduce the cost of technology development.

# VI. Advanced Logic and Connectivity (WP3) – Connectivity (T3.2)

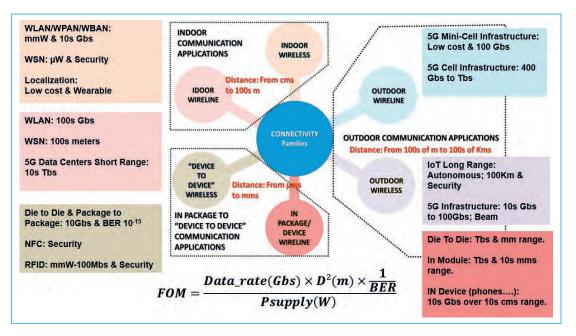

Connectivity functions are everywhere, making the link between all other electronic functions. From the sensors and actuators to the processors and microcontrollers, from the sensor nodes to the gateways, from the gateways to the cells from the cells to the data centres, and all over the world. Inside each of these units, the connectivity links the computers to the memories, the cores of multicores in High performance computing applications, and the peripheral devices to the central computing units.

The connectivity functions can be differentiated depending on the range and the nature. The nature of such function are wireless (in radio frequency mmW, THz bands, or visible light), or wireline (in copper or optical fibre). The range of such functions can be sorted out depending on the distance, the ultra-short range, is in the  $\mu$ m to cm distance; the short range is under 100 m, while the long range covers distances over 100 m.

Presently the largest connectivity market activity is dedicated to data communications, especially for cellular (WAN), WLAN, WPAN, NFC, and incoming WSN and IoT communications. We can distinguish two other market areas, especially in Europe, even if they use, or are be connected to the first one: the automotive market which is at the beginning of the autonomous vehicle revolution, and the "health & security" market which will transform drastically our way of life in the next decades.

In the data communication field, we can distinguish three main families using the link distance criteria, the outdoor and cellular, for example 5G and future generations, the indoor communication mainly represented today by the Wi-Fi links, and a third which is not visible to the consumer, which can be called the In Devices one, or the communication between dies and packages in an equipment.

# Main concepts on Connectivity

The examined main concepts within the roadmap sub chapter on Connectivity are 1+2) the Outdoor Wireless and Wireline Applications, 3+4) the Indoor Wireless and Wireline Applications, 5) the Device to Device Wireless Applications and 6) the In Package/Device Photonics Wireline Applications (s. Figure 01.6).

Recommendations for Connectivity

Main recommendations for the Task

- » Evaluation of the Connectivity figures of merit (FoM) for each concept.

- » Reinforce the Indoor Short range Roadmap.

- » Refine the technology request for each application.

- » Define a complete Market analysis for each concept.

Main recommendations for technology research:

- » Antennas & Passives: On demand re-configurable and tuneable Antennas and Passives, very compact and massive MIMO antennas, with beamforming systems and very high antennas' directivity for all the used band, 0–6GHz and mmW. Work may address metamaterials, NEMs, MEMs and integrated passives technologies, packaging and modules, design, systems and microsystems.

- » Transceivers & Front End Radio: High Data Rate: Up to 100GHz and up to THz Transceivers, stable and accurate local oscillators, and antennas' interfaces targeting high and agile spectrum usage, with wider communication bands, allowing full-duplex communications and solving interference management, with on demand new PHY waveforms generation. Work may address new generation of nm CMOS, beyond CMOS, and mixed Silicon-III-V technologies, NEMs, MEMs, and new physics devices, combined with new design methodologies, modelling and wireless long range, short range or wave guided systems.

- » Transceivers & Front End Radio: Low Power Radio: Ultra-low power transceivers for WSN and IoT Networks, with µW consumed power objectives. Work may address Wake-Up Radio, ultra-stable ultra-low power time reference, charge transfer, or timefrequency modelling and design methodologies, CMOS, Beyond CMOS, NEMs MEMs, and new physics devices, wireless, including ultrasonic, or silk guided systems.

» Wireline: Low cost 1300 nm and 1500 nm laser sources, optic modulators, LEDs, and PIN diodes, with their electrical interfaces, drivers and Trans impedance Receivers, for modulations giving 400 Gbs to Tbs. Work may address photonics integrated components, including laser and VCSELs, copper wireline interfaces, 3D packaging methodology, multi-physics modelling and simulation, CMOS beyond CMOS, and low cost exotic More than Moore processes.

# VII. Functional Diversification (WP4) – Smart Sensors (T4.1)

Global challenges for today's technology concern more sustainable, ICT-enabled strategies for healthcare, energy and environment. The role of edge-of-the cloud devices and of the generated big data are expected to drive the creation of new ecosystems and include 11 % of the world economy by 2030.

The technology-market developments moved from a Processing Information "Moore" age (from the 80's to 2010) to a present Sensing Interaction in the "More than Moore" age (from 2010 to 2030, exploiting mobile computing and communication technologies) and, the expectations for the future are about an Actuating Transformation "Beyond Moore" age (beyond 2030, with smart cities, smart home and autonomous vehicles and Industry 4.0 driving the application scenarios). This means that the technology is moving from simple sensing to smart sensing in almost every object, enabling new classes of services and applications.

The challenge of producing a European smart sensor roadmap is broad, complex and diversified because sensing technologies are very diverse and not driven just by scaling and costs. The exponential growth of the importance of smart sensors was first pointed out in Europe and worldwide by the FET Flagship initiative Guardian Angels for a Smarter Life in 2011, a project

# Figure 1.06: Next 5 years Connectivity Challenges

# Figure 1.07: Smart Sensors – Roadmap

that proposed roadmaps for energy efficient smart sensors in a perspective of 10 years. Only later some industries came with roadmaps for the so called 'Trillion of sensors planet'. This means that Europe played a pioneering role in understanding and predicting the importance of smart sensors to support edge of the cloud applications in the future economy.

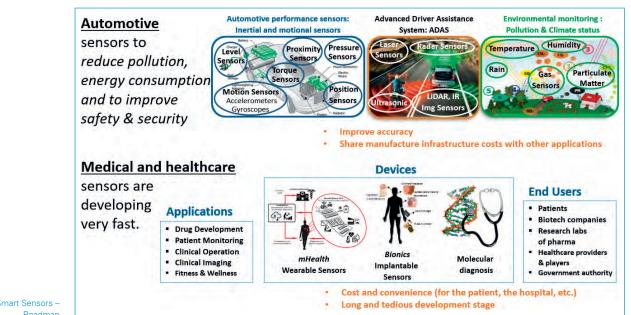

Among many domains for smart sensor applications, NEREID has chosen to focus on two main fields: (i) healthcare and (ii) automotive, as application drivers. These two fields have a high relevance for European industry and research (s. Figure 1.07).

In the healthcare sector European countries are coming second after US, while in automotive, Europe dominates the autonomous vehicle market. Moreover, the European leadership in automotive is expected to be reinforced in the coming 5–10 years thanks to the presence of major technology manufacturers, early commercialization of automated vehicles and public organizations supporting the advancement of these vehicles. In addition, most of the sensors types and challenges outside these fields are similar and relevant for industrial segments such as consumer electronics (MEMS accelerometers, magnetic, chemical and gyroscopes), industrial (image sensors), environmental (air quality gas sensors) and defence (also LiDAR sensors).

Overall, connected objects (as part of Internet of Things, IoT), big data, software and algorithms, zeropower or self-powered sensors, sensor fusion, wireless sensor networks and system-in-package are all important topics for a more complete sensor roadmap.

# Main concepts on Smart Sensors

The examined main concepts within the roadmap sub chapter on Smart Sensors are 1) Motion Sensors, 2) Pressure Sensors, 3) Advanced Drive Assistance Systems (ADAS), 4) Radar Sensors, 5) Pollution/Air Quality Monitoring based on gas sensors, 6) Physiological Signal Monitoring, 7) Implantable Sensors: Bionics and 8) Molecular Diagnostics.

# Recommendations for smart sensors

General recommendations for the smart sensors in the automotive and in the medical/healthcare segment described previously are the following:

- » Shared manufacture infrastructure cost with other applications (e.g. between automotive and consumer), improved processes that further lower cost (like CMOS MEMS) or the creation of new devices with added value (e.g. software embedded within the sensor to deliver higher level functions) are some ways to improve margins as for example in MEMS market.

- » CMOS integration, compatibility and readout circuitry and new enabling technologies keep coming. However, integration becomes more challenging and reliability gets less predictable. It is predicted that smart sensors will remain as close as possible to CMOS standards.

- » Stability and reliability are the two most important features for the industrial take up of smart sensors. High reproducibility, ppb detection limits due to concentration, signature for functionalization, form factor and the power consumption of the platform are secondary characteristics that have to be taken into consideration for the sensor development. Furthermore, selectivity is not the most important feature for sensing.

- Regulations and guidelines are required to limit vehicle emissions and thus further reduce pollution and dependence on oil, to establish emission standards that dictate the limits of pollutants (CO<sub>2</sub>, NOx, etc.) in indoor and outdoor air environments. Vehicle safety regulations are also a priority for Europe to reduce 50 % of road accidents (cars, bicycles, pedestrian, etc.) by 2030. On the other hand, the

different regulations and languages among national health organization are limiting to develop the European medical market. Medical devices development including market introduction is very time consuming (minimum 10 to 15 years), expensive and difficult nowadays, related to the long and tedious development stage, followed by the high cost of clinical validations, and the difficult process of CE labelling / FDA approval in case of novel device concepts (non-standard validation tests). The creation of a European excellence consulting and advising clinical validation centre would support the development of novel medical devices and reduce the time to market for them.

- » Assembly testing, standards and metrology are crucial for the future success of smart sensors. There is a lack of metrology standards, commonly it is difficult to interpret which results in time consuming investigations.

- » Auto-calibrated, self-calibrated or an easy way of sensor calibration is not a common feature for the sensors in the market yet. However, this is highly interesting and required for future industrialization and a long-term sensor stability. As an example, CMOS capacitive sensors have the advantage that they do not need to be calibrated but they might have a poor sensitivity.

- The maturity level of each sensor technology has to be assigned, estimating than a technology with a TRL higher than 6 would result to a product into market in less than 3 years approximately. The standards will be pushed very high in the different roadmaps but without excluding any technology for the next 10-year long term projection. The reason is that some application domains need mostly performance as in military while for others cost is the most important factor or the repeatability, stability, reliability and yield for huge volume productions. A clear TRL correlation with technologies needs to be established.

Thus, some of the smart sensor identified gaps by 2030 concern: manufacturability and cost (hybrid inte-

gration), low power consumption (energy efficiency), robustness of design and in production, as well as reliability.

# VIII. Functional Diversification (WP4) – Smart Energy (T4.2)

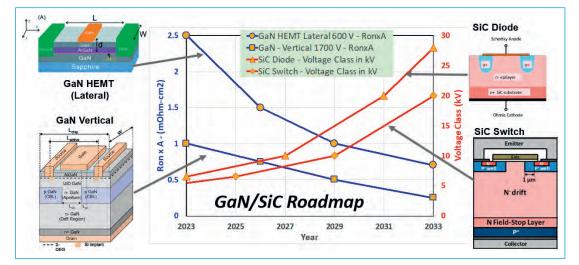

Power devices based on wide bandgap semiconductors (WBS), like GaN, SiC,  $Ga_2O_3$ , are poised to play an important role in future power electronics systems. WBS has a high breakdown strength and, in the case of GaN, allows for fabrication of high electron mobility lateral transistors, for which the electron mobility is not degraded as would be the case for traditional silicon MOSFETs. These facts combined allow the fabrication of devices which have orders of magnitude better trade-off between the specific on-resistance of the devices and the breakdown voltage.

The roadmap for devices has been set up along three tracks, the first considers the GaN based devices starting from materials towards integration. The second track is related to the evolution of SiC (again from materials to applications). Finally future material systems (AIN, Diamond, and  $Ga_2O_3$ ) are considered which could offer benefits over the actual WBS in certain domains.

# Main concepts on Smart Energy

The examined main concepts within the roadmap sub chapter on Smart Energy are 1) GaN-devices and substrates, 2) SiC-based substrates and 3) Alternative Wide Bandgap Semiconductors (s. Figure 1.08).

# Recommendations for Smart Energy

- » Apart from WBG device development the WBG system integration is necessary to exploit the full potential,

- Packaging and system integration technologies enabling low parasitic inductances to master EMC issues,

- Packaging and system integration technologies enabling reliability at higher temperatures,

Figure 1.08: Smart Energy -Roadmap

Figure 1.09: Energy for autonomous systems – Roadmap of main concepts

- Handling higher voltages on package/module level and system level: SiC in medium voltage (MV) applications e.g. in traction and industry,

- » Low inductance packaging and integration technologies: power PCB with chip embedding, system-inpackage (SIP), switching cell in a package,

- Passive components for fast switching: mainly inductors, reduce losses at high switching frequencies, thermal management of (integrated) passives,

- » Characterisation, testing, modelling and reliability analysis of WBG packages, modules and converters.

# IX. Functional Diversification (WP4) – Energy for autonomous systems (Sub T4.2)

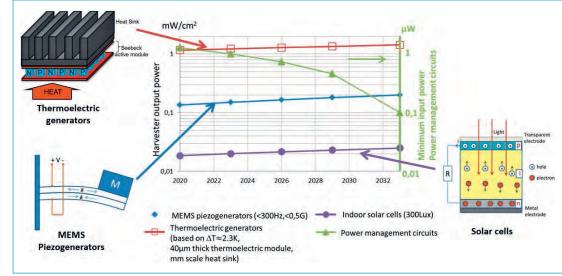

As the communicating systems market is booming, the role of energy harvesting (EH) will be growing. Indeed, the number of connected devices is expected to increase by a factor of 200, while the number of mobile phones is just expected to increase by a factor of three. Connected devices are going to be used more and more in several fields such as healthcare, wearables, home automation, etc. The Internet of Things (IoT) market grows considerably leading also to the boom of connected devices, and so highlighting the importance of energy needed to supply them in view of the limitations of current battery technology. In this particular case, NEREID is focusing on small connected devices with low power consumption below a few mW (or even a few tens of  $\mu$ W).

Different wasted energy sources can be exploited and converted into electricity: Sun or artificial light, heat, mechanical movements and vibrations... Moreover this converted energy needs to be used and transferred wisely to sensors, microcontrollers or other electronic components included in the system. Thus power management circuitry becomes also an essential element.

In this Mid-Term roadmap report, we have assessed several promising technologies for EH and power management circuits including photovoltaic cells for outdoor/indoor light EH, mechanical EH based on two concepts: piezoelectric materials and electrostatic energy conversion, and finally the power management circuits. Other promising technologies will be covered in the second half of the project.

# Main concepts on Energy for Autonomous Systems

The examined main concepts within the roadmap sub chapter on Energy for Autonomous Systems are 1) mechanical energy harvesting: electrostatic transduction, 2) mechanical energy harvesting: piezoelectric transduction, 3) thermal energy harvesting, 4) photovoltaic energy harvesting, and 5) micro-power management (s. Figure 1.09).

# Recommendations for Energy for Autonomous Systems

In general, the development of applications is the key to success for EH. IoT and energy harvesting are application-driven today, so projects should mainly focus on the development of a complete application (from harvesting to the use case). Concerning the concepts covered so far in this Mid-Term roadmap (vibrational, solar, thermal EH and power management), the improvement of their performance and efficiency is as important as the development of "green" materials, replacing toxic/rare materials used nowadays (lead based piezo electrics, BiaTea for thermoelectrics). The use of nanotechnologies is foreseen to increase the performance of all the concepts in general. Flexible and low cost approaches for wearable applications should be developed as well. Increasing the bandwidth at a low frequency target (below 100 Hz) will help to fit applications for vibration based mechanical energy harvesters. Concerning indoor photovoltaic applications, adapted structures and materials (light intensity and spectra...) should be developed. Concerning power management circuits, it would be key to investigate size reduction of inductors, to enhance the efficiency of inductor-less power converter circuit topologies, to develop planar alternative to inductors and to tune microelectronic process parameters and technologies to reduce leakage for reduced power consumption and allowing low input voltages.

# X. System Design and Heterogeneous Integration

Building a roadmap for System Design and Heterogeneous Integration is a tough challenge, because of the variety of applications involved, demanding for very different requirements, sometimes even contrasting in terms of values, limits and importance. Several roadmapping attempts have been done in the past. The first example is the 2007 revision of ITRS where some quantitative Figures of Merit (FoM) were given in terms of percentage of improvement over standards or targets. In the following ITRS revisions of 2009 and 2011, quantitative FoM have been replaced by bar charts, related to the topic's development status with respect to the time horizon.

It is therefore justified to consider a new approach for roadmapping System Design and System Level Applications, which goes beyond the simple inclusion of static numerical tables. The NEREID approach is to build a general Top-Down description of the requirements (a hierarchical map) that has to be met in a Bottom-Up process, with concepts, methods, values and expectations strictly related to the application of reference.

In the first version of the roadmap chapter on System Design and Heterogeneous Integration, concepts are split in the two parts of the headline (System Design and Heterogeneous Integration) allowing a better initial orientation, improved focusing opportunities and effectiveness in deciding. However, the final goal is to generate a unique roadmap in the second version (that will be released next year), merging the different contributions.

# Main concepts on System Design and Heterogeneous Integration

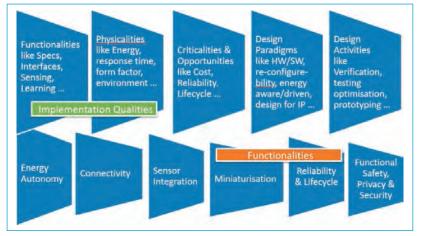

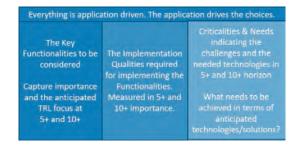

The examined main concepts within the roadmap chapter on System Design and Heterogeneous Integration are 1) System Design Concepts, 2) "Physicalities", 3) Criticalities & Opportunities, 4) Design Paradigms, 5) Design Activities, 6) Energy Autonomy, 7) Connectivity, 8) Sensor Integration, 9) Reliability, Functional Safety & Security and 10) Ubiquitous/Pervasive. Figure 1.10 and 1.11 show, how these concepts are distinguished between implementation qualities and functionalities which offer the choices in system design.

Figure 1.11 illustrates how application drives the choices in system design by the implementation qualities and functionalities.

# Recommendations for System Design and Heterogeneous Integration

In the following, the most important recommendations related to System Design and Heterogeneous Integration are summarised:

Europe has an excellent opportunity to drive the increase in System Knowledge bringing Europe to a leading position for System Level Applications **Figure 1.10:** Implementation Qualities and Functionalities offer the choices for the system

- » Add Software in the middle, starting from the application.

- » The value is not in the device itself, but in system integration and in the related data, the Information is at systemic level.

- » Check the need for validation: which is the level of robustness that is acceptable

- » Take care, where to position the intelligence.

- » The future is to move from Embedded Computing to Embedded Intelligence and towards Smart Adaptive Systems.

- » Definition of standards for interoperability is important. Openness of standard cannot prevent monetisation.

- » Take care of Re-Usability / Reconfigurability and also "zero maintenance"

- » Realise Software-like re-programmability with (almost) hardware like efficiency

- » Consider Automated Design Space Exploration and automated design decisions.

- » Try to move from Connected Devices to Distributed Embedded Systems (System of Systems) and take care of Network Synthesis as network is a design dimension

- » Environment has to be considered as part of the system and needs to be taken into account

- » Ensure Energy Autonomy by pushing limits of energy harvesters to their fundamental optimum and by integration of miniaturised storage with highenergy density and high-power capability

**Figure 1.11:** Application drives the choices for the system

» Consider Power Management in a holistic approach integrating hybrid energy harvesting and aiming at reducing consumption for each layer and as a whole (consumption when is necessary only)

The strategic conclusion is that for Europe it is a very good opportunity to drive an increase in System knowledge. In Europe many important stakeholders are present, with original know-how, enabling Europe to become a leading supplier of System Level Applications.

# XI. Equipment and Manufacturing Science (WP6)

NEREID's approach to create a comprehensive "Nano-Electronics Roadmap for Europe" is quite a challenge, in particular for WP6, where all other topics of the roadmap, e.g. Beyond CMOS, Nanoscale FET etc., have to be considered from equipment, materials and manufacturing perspective. In this first version, WP6 - Equipment, Materials and Manufacturing Science is mainly concentrating on equipment and materials, but does also reflect some manufacturing related aspects as well. The second version, which will be released next year, will include more manufacturing related topics.

# Authors

J. Ahopelto VTT Microsystems and Nanoelectronics Espoo, Finland G. Ardila,

INP Grenoble, France F. Balestra, INP Grenoble/CNRS, France D. Belot, CEA-LETI, Grenoble, France D. Demarchi,

> Politechnico Torino, Italy S. De Gendt,

IMEC, Leuven, Belgium G. Fagas,

Tyndall, Cork, Ireland M. Fernandez-Bolaños, EPFL, Lausanne Switzerland

> D. Holden, CEA-LETI, Grenoble, France

G. Meneghesso, IUNET, U Padova, Italy

A. Mocuta, IMEC, Leuven, Belgium

M. Pfeffer, Fraunhofer Gesellschaft, Erlangen, Germany

> R. M. Popp edacentrum GmbH Hannover, Germany

E. Sangiorgi, U Bologna/Sinano, Italy

C. M. Sotomayor Torres Catalan Institute of Nanotechnology Barcelona, Spain The first version was drafted after several consultations with technical experts of WP6 during specific domain workshops, by analysing the available information of the other work packages and by reviewing the application oriented talks presented during the first and second general workshops. As a first attempt, no Figures of Merit were given in the context of equipment and material. Nevertheless, there are indications on two different time horizons, when corresponding equipment and materials have to be available on the market for the different technologies.

# Main concepts on Equipment and Manufacturing Science

The main concepts within the roadmap chapter on Equipment and Manufacturing Science are 1) More Moore, 2) More than Moore, and 3) Manufacturing Science.

# Recommendations for Equipment and Manufacturing Science

- » Concurrent WP's (WP2 WP5) shall analyse their domains in view of the presented applications and derive immediate and long-term requirements in terms of materials, processes and manufacturing needs.

- » Given the worldwide effort on materials, processes and manufacturing in the domain of More Moore, the imminent needs of European application domains are covered. However, more specific needs in the other NEREID domains need to be identified.

- Cover activities in WP6 roadmap where Europe is leading in terms of materials, processes and manufacturing, but where the demand from application side is stronger outside of Europe (e.g. EUV litho)

- » Cover activities in WP6 where application wise Europe is leading, but where specific needs for materials, process and manufacturing require continued attention (e.g. OLED)

- » Build synergies with ITRS/IRDS activities whenever possible, in particular for the section manufacturing science.

# **XII. General Recommendations**

The aim of future research activities in the field of Nanoelectronics is to further develop Europe's excellence to support technology development and innovation and strengthen its competitiveness and market leadership of the related industries. Research and innovations in Nanoelectronics, covering the medium to long-term impacts, are crucial to the European technological leadership in ICT. They are complementary to ECSEL activities mainly devoted to short term applications. The main recommendations for the Nanoelectronics Technologies covered by NEREID have been mentioned above in close connection with the characterization of the roadmap's technology sectors.

# XIII. General Conclusion

The first 18 months of the NEREID Project was very successful and led to a preliminary mid-term Nanoelectronics Roadmap including all important technologies for many applications representing large future markets. The NEREID Roadmap took into account the specifics of the European industrial and academic landscape and will be very useful for equipment, semiconductors and application developments.

The project supported the participation of more than 100 application and technology experts from leading research organizations in industry and academia in General and Domain Workshops. These Workshops allowed the consortium to better define the technology roadmap in terms of applications requirements (in the fields of Energy, Automotive, Medical/Life science, Security, IoT/Smart connected objects, Mobile convergence, Digital Manufacturing) and technology evolution (Advanced Logic and Connectivity, Functional diversification, Beyond-CMOS, Heterogeneous Integration and System design, Equipment, Materials and Manufacturing Science), and to discuss the convergence between applications and technologies.

This common work between technology and application experts is leading to the early identification of the main challenges and the most promising technologies needing additional R&D activities. These will be prerequisites for a prosperous future of European electronic components and systems companies leading to a strong European economy and society.

# XIV. Roadmap Release

The development of the first version of the roadmap referred to as Mid-Term Roadmap has been published during the ECCIRC/ESSDERC conference, where NEREID (in cooperation with the European Institute of Nanoelectronics SINANO (www.sinano.eu)) was invited to hold a workshop within the conference schedule. In this workshop, the NEREID project reported on its recent findings documented in the Mid-Term Roadmap and faced a vivid feedback situation with the audience of about 40 participants of the workshop aiming to verify the current results by discussing especially controversial points.

At the same time on September 11, 2017, the Mid-Term Roadmap has then been published on the NEREID website (https://www.nereid-h2020.eu/). The roadmap is available for free download after filling in a web form, which collects the contact information. In this way, NEREID is enabled to contact the readers of the Mid-Term Roadmap in order to ask for their feedback. Furthermore, the Mid-Term Roadmap has been presented in the Speaker's Corner during EFECS 2017 in December 2017 in Brussels.

# Acknowledgements

This article has been condensed mainly from the NEREID Mid-Term Roadmap [1]. The authors are grateful to all the contributors of this document. However, the responsibility for the content of this article lies with the authors. Thanks are extended to all speakers and discussants in the various NEREID workshops who gave their views and time. The support of the EU ICT-CSA project NEREID (grant agreement No 685559) is gratefully acknowledged.

Download of the NEREID MidTerm Roadmap is possible at the NEREID website: https://www.nereid-h2020.eu/roadmap

NEREID invites all interested experts to join the elaboration of the roadmap. Just contact Ralf Popp at popp@edacentrum.de.

# References

F. Balestra et. Al. "NanoElectronics Roadmap for Europe", Sept. 2017, https://www.nereid-h2020. eu/roadmap

# Cont@ct (NEREID)

Francis Balestra fon: +33456529510 balestra@minatec.grenoble-inp.fr Ralf Popp fon: +49 (511) 762-19697 popp@edacentrum.de

### Ansprechpartner im edacentrum

Prof. Dr. Wolfgang **Rosenstiel** | Vorstand fon (0 70 71) 2 97 54 82, (Ro) rosenstiel@edacentrum.de

Prof. Dr. Wolfgang **Nebel** | Vorstand fon (04 41) 9 72 22 80, (WN) nebel@edacentrum.de

Dr. Jürgen **Haase** | Vorstand fon (05 11) 7 62 – 1 96 98, (Haa) haase@edacentrum.de

Maren **Sperber** | Sekretariat fon (05 11) 7 62 – 1 96 99, (Sp) sperber@edacentrum.de

Dipl.-Ing. (FH) Peter **Neumann** | Projektmanagement fon (05 11) 7 62 – 1 93 83, (Ne) neumann@edacentrum.de

Dipl.-Ing. Ralf **Popp** | Öffentlichkeitsarbeit (Leitung) fon (05 11) 7 62 – 1 96 97, (Pp) popp@edacentrum.de

Dr. Dieter **Treytnar** | Öffentlichkeitsarbeit fon (05 11) 7 62 – 1 96 87, (Tr) treytnar@edacentrum.de

Dr. Andreas **Vörg** | Consulting fon (05 11) 7 62 – 1 96 86, (AV) voerg@edacentrum.de

# Impressum

# Herausgeber

edacentrum e.V. Schneiderberg 32 30167 Hannover fon (05 11) 7 62 – 1 96 99 fax (05 11) 7 62 – 1 96 95 www.edacentrum.de info@edacentrum.de

# Redaktion Ralf Popp (V.i.

Dieter Treytnar newsletter@edacentrum.d

# Autoren

Ahopelto, Ardila, Balestra, Demarchi, De Gendt, Fagas, Fernandez-Bolaños, Fürtig, Gläser, Grimm, Haase, Holden, Meneghesso, Mocuta, Neumann, Nitsche, Olbrich, Pfeffer, Pfitzner, Popp, Radojicic, Sangiorgi, Sotomayor Torres, Speicher, Treytnar, edacentrum, ANCONA, AENEAS, Audi, Bosch, ECSEL, ESD Alliance, Hella, Fujikura, Infineon, Intel, Microchip, NEREID, PENTA

Wir bedanken uns herzlich bei allen Autoren, die bei der Erstellung des Newsletters geholfen haben.

Satz, Grafik und Druck stm|Media GmbH, N. Möller, M. Hoinkis & D. Pau Druckhaus Köthen GmbH, Köthen S.-A.

Fotos Gläser, Popp, Treytnar, Wille

# Ausgabe

Der newsletter edacentrum 01/02 2017 ist erschienen am 22. Dezember 2017, Auflage: 1050

# Redaktionsschluss

Der nächste Newsletter erscheint 2018 Redaktionsschluss ist am 18. April 2018.

Alle im "newsletter edacentrum" abgedruckten Beiträge sind urheberrechtlich geschützt. Alle Rechte, auch Übersetzungen, sind vorbehalten. Reproduktionen, gleich welcher Art (Mikrofilm, Fotokopie oder Erfassung in Datenverarbeitungsanlagen), nur mit schriftlicher Genehmigung des Herausgebers.

Für den Fall, dass im "newsletter edacentrum" unzutreffende Informationen enthalten sein sollten, kommt eine Haftung nur bei grober Fahrlässigkeit in Betracht.